अत्याधुनिक चिप्स बनाने के लिए फाउंड्रीज़ के पास सबसे महत्वपूर्ण उपकरण एक एक्सट्रीम अल्ट्रावॉयलेट (ईयूवी) लिथोग्राफी मशीन है। जो चीज़ इसे इतना महत्वपूर्ण बनाती है वह यह है कि लिथोग्राफी मशीन एक चिप के लिए सर्किटरी डिज़ाइन को सिलिकॉन वेफर पर उकेरती है। जब आप इस बात पर विचार करते हैं कि 3nm प्रक्रिया नोड का उपयोग करके बनाए गए एक एप्लिकेशन प्रोसेसर (AP) के अंदर 20 से 30 बिलियन ट्रांजिस्टर हो सकते हैं और इससे भी अधिक, EUV को 13.5nm की बेहद छोटी तरंग दैर्ध्य का उपयोग करके इन डिज़ाइनों को प्रिंट करने के लिए आवश्यक है, जिससे चिप के जटिल पैटर्न को वेफर पर मुद्रित किया जा सके।

EUV मशीनों की लागत $150 मिलियन और उससे अधिक है। इनका निर्माण दुनिया में केवल एक ही कंपनी द्वारा किया जाता है

ईयूवी लिथोग्राफी के निर्माण से पहले, डीप अल्ट्रावॉयलेट (डीयूवी) लिथोग्राफी थी जिसकी तरंग दैर्ध्य 193 एनएम थी। DUVs ने फाउंड्रीज़ को 10nm जितनी कम प्रक्रिया नोड का उपयोग करके चिप्स बनाने की अनुमति दी और EUV को 7nm, 5nm, 3nm और 2nm के प्रक्रिया नोड्स पर एक एकीकृत सर्किट (IC) का उत्पादन करने के लिए नियोजित किया गया है। जैसे-जैसे प्रक्रिया नोड संख्या घटती जाती है, ट्रांजिस्टर का आकार घटता जाता है जिससे उनमें से अधिक को चिप के अंदर फिट होने की अनुमति मिलती है। IC के अंदर जितने अधिक ट्रांजिस्टर होंगे, वह उतना ही अधिक शक्तिशाली और ऊर्जा-कुशल होगा।

लो-एनए ईयूवी के लिए ईयूवी की वर्तमान कीमत $150 मिलियन-$200 मिलियन है। भविष्य के अत्याधुनिक चिप्स के उत्पादन के लिए नवीनतम पीढ़ी की ईयूवी मशीनों, हाई-एनए ईयूवी की आवश्यकता होगी, जिसकी लागत $350 मिलियन से $380 मिलियन है। पहले वाले के लिए .33 की तुलना में बाद वाले का संख्यात्मक एपर्चर .55 है। यह हाई-एनए मशीन को छोटी विशेषताओं (जैसे सर्किटरी पैटर्न) को अधिक रिज़ॉल्यूशन में प्रिंट करने की क्षमता देता है।

हाई-एनए ईयूवी मशीन के बिना, फाउंड्रीज़ को मल्टी-पैटर्निंग नामक तकनीक का उपयोग करना होगा जिसमें डिज़ाइन को कई पैटर्न में विभाजित करना शामिल है जो कई बार मुद्रित होते हैं। इससे पैदावार ख़राब हो सकती है क्योंकि इसे कार्यान्वित करने के लिए प्रत्येक प्रदर्शन से पहले सही संरेखण की आवश्यकता होती है।

दुनिया में केवल एक ही कंपनी है जो ईयूवी मशीनें बनाती है, डच फर्म एएसएमएल। कंपनी ने अमेरिकी प्रतिबंधों का पालन किया है और ईयूवी लिथोग्राफी को चीन से बाहर रखा है। यह चीनियों को अत्याधुनिक चिप्स बनाने में मदद नहीं कर सकता है, लेकिन सबस्ट्रेट नाम की एक अमेरिकी स्टार्ट-अप कंपनी ने एक्स-रे लिथोग्राफी (एक्सआरएल) तकनीक विकसित की है जो कण त्वरण के आधार पर प्रकाश स्रोत प्रदान करती है।

सब्सट्रेट को भविष्य में मूर के नियम का विस्तार करने की उम्मीद है

तभी कण त्वरक का उपयोग करके उपपरमाण्विक कणों (जैसे प्रोटॉन, इलेक्ट्रॉन और आयन) की गति और ऊर्जा को लगभग प्रकाश की गति तक बढ़ा दिया जाता है। सबस्ट्रेट का कहना है कि इसका लक्ष्य ऐसे रिज़ॉल्यूशन प्रदान करना है जो ASML की 2nm-क्लास प्रक्रिया से मेल खाते हों। कंपनी का कहना है कि उसके उत्पाद प्रतिस्पर्धा की तुलना में सस्ते होंगे और 2030 से पहले बेहतर रिज़ॉल्यूशन पेश करेंगे।

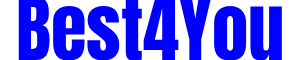

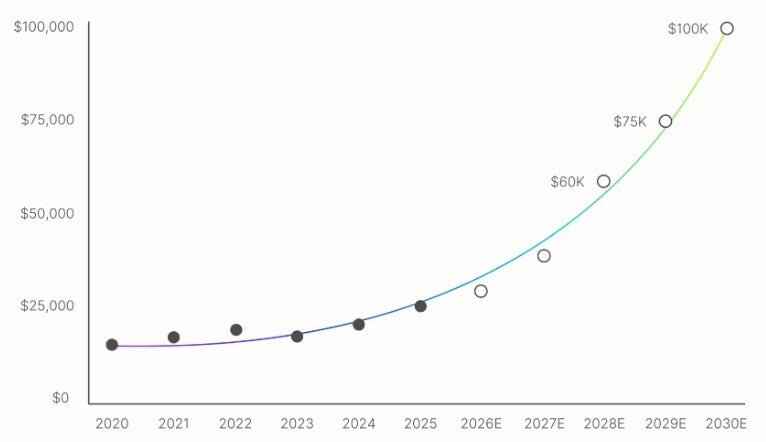

चार्ट अत्याधुनिक चिप्स के लिए अतीत, वर्तमान और अपेक्षित भविष्य के सिलिकॉन वेफर की कीमतों को दर्शाता है। | छवि क्रेडिट-सब्सट्रेट

सबस्ट्रेट का कहना है कि “हमारे त्वरक सूर्य की तुलना में अरबों गुना अधिक तेज प्रकाश उत्पन्न करने वाली किरणें सीधे हमारे लिथोग्राफी उपकरणों में डालते हैं, जिनमें से प्रत्येक उन्नत सेमीकंडक्टर चिप्स के लिए आवश्यक सबसे छोटी सुविधाओं का उत्पादन करने के लिए एक पूरी तरह से नए ऑप्टिकल और उच्च गति यांत्रिक प्रणाली का उपयोग करता है। जबकि वर्तमान दृष्टिकोण अपनी सीमा तक पहुंच रहे हैं, जिससे लागत और जटिलता बढ़ रही है, हमारे सभी आविष्कार आने वाले वर्षों के लिए मूर के कानून का विस्तार करने के लिए मिलकर काम करने के लिए डिज़ाइन किए गए हैं।”

मूर का नियम इंटेल के सह-संस्थापक गॉर्डन मूर द्वारा किया गया अवलोकन है जो कहता है कि एकीकृत सर्किट पर ट्रांजिस्टर घनत्व हर दूसरे वर्ष दोगुना हो जाता है। ट्रांजिस्टर घनत्व प्रति वर्ग मिलीमीटर ट्रांजिस्टर की संख्या को मापता है। सबस्ट्रेट जो कह रहा है वह यह है कि इसकी एक्स-रे लिथोग्राफी (एक्सआरएल) भविष्य की प्रक्रिया नोड्स और अधिक जटिल डिजाइनों के लिए काम करेगी।

सब्सट्रेट सेमीकंडक्टर उत्पादन में अमेरिका को प्रभुत्व में लौटा रहा है

हमने आपको रॉक के नियम के बारे में कभी नहीं बताया है जो कहता है कि एक अग्रणी सेमीकंडक्टर निर्माण सुविधा के निर्माण की लागत हर चार साल में दोगुनी हो जाती है। उदाहरण के लिए, ऐसी सुविधा की लागत 2010 की शुरुआत में $5 बिलियन थी और आज इसकी लागत लगभग $25 बिलियन है।

सब्सट्रेट का कहना है कि 2030 तक, 2nm वेफर्स के लिए मौजूदा $30,000 की तुलना में प्रत्येक वेफर्स की कीमत $100,000 होगी। प्रत्येक फैब्स की लागत $50 बिलियन से अधिक होगी। सबस्ट्रेट के अनुसार, इस परिदृश्य में “केवल सबसे बड़ी कंपनियां ही अग्रणी सिलिकॉन का लाभ उठाने वाले उत्पादों का निर्माण करने में सक्षम होंगी। इस स्केलिंग का अर्थशास्त्र भौतिकी की तुलना में अधिक कठिन है। यह आर्थिक मॉडल टूटा हुआ लगता है।”

यहीं पर सबस्ट्रेट आता है। कंपनी की वेबसाइट कहती है कि उसके पास अत्याधुनिक चिप्स के निर्माण की लागत को कम करने का एक “मार्ग” है। दशक के अंत तक, सबस्ट्रेट का कहना है कि वह अंतिम उपयोगकर्ताओं के लिए $100,000 की तुलना में $10,000 के करीब लागत वाले वेफर्स का उत्पादन करेगा। और सेमीकंडक्टर उद्योग के लिए यह जितना अच्छा हो सकता है, सबस्ट्रेट का कहना है कि इसकी तकनीक “सेमीकंडक्टर उत्पादन में संयुक्त राज्य अमेरिका को प्रभुत्व में वापस ला रही है।”